# Examination of Crosstalk in Transmission Lines

Prepared by: Amanda J Penning

*Faculty Advisors:* Dr. Tomas Montoya REU Site Director, Improving Communications and Lives

Dr. Charles Tolle Associate Professor, Department of Electrical Computer Engineering

> Dr. Alfred Boysen Professor, Department of Humanities

> > Mr. Steven Lawler Electronics Specialist

Program Information: National Science Foundation Grant NSF #1359476

Research Experience for Undergraduates Summer 2014

South Dakota School of Mines and Technology 501 E. Saint Joseph Street Rapid City, SD 57701

# **Table of Contents**

| Abstract 3                          |

|-------------------------------------|

| 1. Introduction 4                   |

| 2. Broader Impact 5                 |

| 3. Procedure                        |

| 3.1 Circuit Design 7                |

| 3.2 Printed Circuit Board Layout 10 |

| 3.3 Daughter Board Design 15        |

| 3.4 Board Milling 17                |

| 3.5 Board Assembly 18               |

| 3.6 Materials 21                    |

| <b>3.7 Equipment 22</b>             |

| 4. Results                          |

| 5. Discussion 23                    |

| 6. Conclusion 24                    |

| 6.1 Future Work 24                  |

| References                          |

| Acknowledgments                     |

#### Abstract

Crosstalk is any phenomenon by which a signal transmitted on one circuit or channel of a transmission system creates an undesired effect in another circuit or channel. Electrical engineers have known about the existence of crosstalk since shortly after the advent of electronic circuits, but it didn't really become a problem until high speed communications became the norm. Newer technology is often difficult to integrate due to the older systems' lack of shielding against crosstalk and the fact that these systems are simply not built to withstand huge amounts of data flow at high speeds. It would be best to replace these older systems, but that is neither conducive nor cheap. The communication systems currently imbedded into society have worked well until this point and they are so ingrained within the infrastructures that it would take years, tens of thousands of man hours, and hundreds of thousands of dollars to replace them. The practical option left is to work within the established systems by incorporating the new technology with the old. This has steered the majority of the research and published works on crosstalk in the direction of ways to avoid or dampen it. It is difficult to find information on how to identify it, what it looks like, how it is created, and most importantly how to avoid its creation when laying out a circuit. What has been published is where crosstalk is often found, for example, at the junctions of new technology and old, as well as where signals come together to be transmitted through connectors into wires. While this is good information to know, what would be more helpful to an Electrical Engineering student would be how to design the circuit without the crosstalk in the first place. This study will intentionally create circuit boards with varying degrees and types of crosstalk in an effort to educate those future students on its appearance on an oscilloscope and other measurement devices along with helping them to conceptualize the differences that board layout and design make.

3

#### 1. Introduction

Crosstalk is a common problem in electronic communications; it occurs when current from an aggressor line is induced across a victim line. The aggressor line is the line in which a current is applied, which creates an electromagnetic field; this field extends out from the copper trace or wire and is dependent upon the amount of current and frequency applied. The victim line is the trace adjacent to the aggressor that falls within that electromagnetic field, which induces current flow; the crosstalk that will be studied. There are two types of crosstalk; common impedance coupling and electromagnetic field coupling. Common impedance coupling occurs when a source circuit and a victim circuit, or several victim circuits, share part of their current path; the most commonly shared path is a return. (5) A common example of this type of crosstalk is the dimming of lights when a large appliance such as a refrigerator switches on. Both the lights and the appliance share a common ground through the electrical wiring of the house. Electromagnetic field coupling, the type of crosstalk this paper will focus on, is further divided into inductive and capacitive crosstalk. Inductive crosstalk occurs when energy is coupled from one circuit to another through the magnetic field generated when current is applied; it usually occurs at instances of low impedance. Capacitive crosstalk occurs when a varying electrical field exists between two adjacent conductors, typically less than a wavelength, inducing a change in voltage across the gap; usually occurs in instances of high impedance. (4) Crosstalk in the victim line is proportional to several factors. The faster the rise time and the larger the voltage change in the aggressor signal, the greater the crosstalk. There are physical considerations as well; the farther from the ground plane or trace and the smaller the distance between the traces will all increase instances of crosstalk. (8) Additionally, crosstalk is affected by factors such as board thickness, trace width and thickness, noise created by other components

populating the board along with the heat generated by those components. Mechanical vibrations also have an effect on signal transmissions; however that topic is outside the scope of this paper.

The goal of this study is to give future electrical engineering students the opportunity to visualize and measure crosstalk using oscilloscopes and other measuring devices. This will be accomplished by developing undergraduate laboratory experiments that will elucidate how trace placement and shielding affects the crosstalk problem.

#### 2. Broader Impact

Today's electrical engineers have a variety of electronic design tools available to them to help with circuit design and board layout. Programs such as Eagle CAD<sup>™</sup> and Altium Designer<sup>®</sup> make it incredibly simple, when compared to beginning standards, to design, route, and mill circuit boards. These companies have invested millions of dollars researching the best practices for circuit layout based on voltage and frequencies applied and they want a return on their investment. Instead of publishing their findings, all of the needed design rules are executed within these programs to avoid issues such as crosstalk. If an engineer makes an error or violates a rule, the program identifies and highlights the violation so that she/he can examine and correct it or override if warranted. Normally, all that needs to be done is alter the placement of the trace or feature slightly and continue working. For a new engineer, the problem comes in when one is trying to find exactly what those rules are. The proprietary nature of the design programs does not permit the common user access to these particulars, for example ideal trace separation for specific frequency ranges, etc. Many of these programs offer a simulation option which tests how the design will perform and what sort of problems may be encountered which is very handy, but in the long run, having the knowledge of proper spacing and shielding beforehand would be very helpful in understanding the process of circuit board design as a whole. Offering students the fundamentals of circuit layout in the beginning will lead them to a greater understanding of their craft and also enable them to be better engineers overall.

#### 3. Procedure

The simple premise is to make a clean measurement of a voltage. But, if the voltage sample line is not shielded properly, it is likely to be bombarded by outside noise at multiple points, adding multiple dimensions of uncertainty. Where did the noise enter and how much degradation did it cause to the sample? How can it be determined if the noise being measured is the noise intentionally created or the noise absorbed from outside sources? Since the goal of the experiment is to measure the intentionally created crosstalk and only the created crosstalk, it is crucial that the input signal, noise and measurement lines are as clean as possible. Therefore, it is imperative that the origin of the signal be securely grounded on both sides along with the entire path the signal takes, including the return signal being measured. That requires designing and building a motherboard that not only allows generation of a good, clean signal but one that minimizes instances of unintentional crosstalk, allows for various crosstalk experiment boards to be installed for comparison, and future expansion to other circuit design issues such as thermal noise, experiments that will be designed in the coming REU years.

# 3.1 Circuit Design

Before any of this can be accomplished, the circuit itself must be designed. First, it was determined what the function of the circuit should be. As explained above, the function is to route clean input signals in, highly protected measurements out, vary the power applied, and maintain the capacity for later expansion. Next, the components that will accomplish these things must be chosen. Two dual 4:1 analog multiplexers (MUX) and a simple resistor bank of varying values enables the student to vary the signal power in both the measurement lines and the noise lines within the circuit. These MUXs act as a multiple position switch connecting

7

multiple input lines one at a time to the output. Two 1.5 GHz ultrahigh speed operational amplifiers (Op Amp) are linear devices that have the properties required for near ideal DC amplification used for signal condition, filtering or to perform mathematical operations. (3) One charge pump voltage inverter generates unregulated negative output voltage from an input voltage based on the charge pump parameters, in this instance +5 volts are inverted into -5 volts. Six capacitors of varying value hold a temporary charge, each acting as a filter, ensuring the device it is partnered with gets a smooth, continuous flow of electricity. There are nineteen resistors total, twelve are used as voltage dividers in the previously mentioned bank in conjunction with the MUXs for power selection. One voltage regulator designed to convert a 5 volt input into a 3.3 volt output. (1) Another voltage regulator that generates a fixed 5 volt output from a 12 volt input. (11) And finally a terminal block to route 12 volts input power.

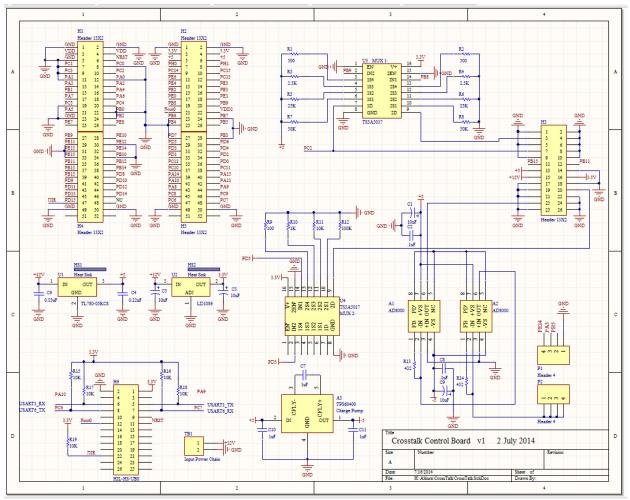

Now that the components are all chosen, the next step is to design an electronic schematic which is the blue print used to identify where and how everything connects together. This is done using Altium Designer® version 2010. First a new file was created and a blank electronic schematic was opened. Then the footprints of the components were placed on the schematic as logically as possible; meaning the components that will be connected electrically are placed as close together on the page as possible. It is not always possible to place everything side by side, space constraints demand being creative with placement at times to get everything to fit. The next step is figuring out how all the components connect together. During this stage all the pins that will be used were assigned a path that the signal will follow, sometimes to another pin on another component, sometimes to ground. This is done by either actually drawing a line from one pin to the connecting pin or by simply assigning it to a net. The net is the same thing as drawing a line but instead of drawing the actual line a 'net,' (a name) is attached to the pin and

8

the corresponding pin is assigned to the same net. This is done for brevities sake and to keep the schematic from becoming a confusing mess of lines. If two pins that will be connected are close to one another a line is used, but in cases where one pin is on one side of the page and the connecting pin is on the other, assigning nets makes connecting the circuit much simpler and cleaner. Depending on the complexity of the circuit, the schematic diagram may be one or several pages long. This circuit was able to be contained to a single page, though it is a bit cramped.

Figure 1: Schematic diagram of mother board

#### **3.2 Printed Circuit Board Layout**

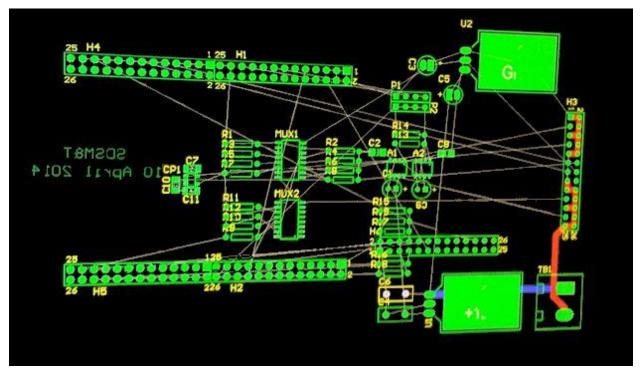

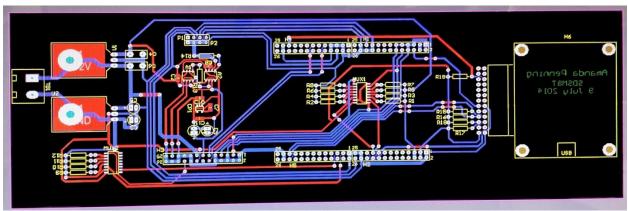

Once the circuit was designed and connected, it was time to layout the physical design of the printed circuit board (PCB). Proper layout of a PCB is a very long and complex process, even with the most carefully planned circuit. Within the same program there is the PCB wizard, when opened it contains the footprints from the schematic at the bottom of the page. (10) The designer must 'grab' these footprints and place them on the board outline again in the most logical way, grouping related components together and lining up the components that can be easily lined up and avoiding placing them too close together. Another polite circuit design practice is to separate the PCB into areas for high, medium, and low frequency circuits. This helps reduce interference from the high frequencies getting into the low frequencies. (7) However, in commercial board design, the smaller the size, the less the cost, so it is important to design as frugally as possible while still maintaining the integrity of the signals. Finally, the voltage that will be applied needs to be considered. For this experiment the 12 volts input power will remain low enough to not be a concern, but in boards that will see voltages greater than 500 volts a special set of standards must be adhered to. (7) Once all the components are placed on the board there are many white lines crisscrossing over one another. This is what is commonly called a 'Rat's Nest.' The white lines in figure 2 denote the electrical connections between pins.

Figure 2: Initial component layout of physical printed circuit board, i.e.: Rat's Nest.

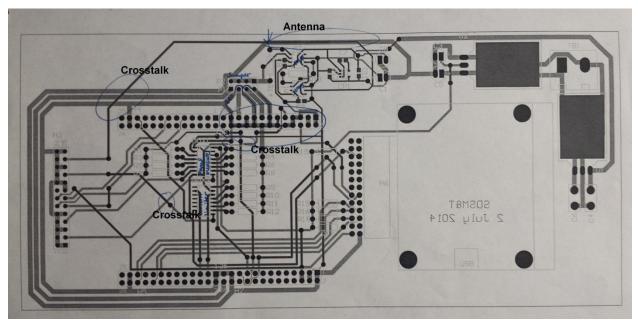

This step takes even more careful planning than schematic design because this is the actual board layout. The layout is critical to the proper performance of the circuit. This is the phase where many beginning engineers make the most grievous of errors such as creating instances of crosstalk by crossing signal lines or routing them parallel to each other without proper spacing and shielding, placing components that create and amplify noise too close to signal lines, and even placing a signal line directly on top of a ground, creating a beautiful little antenna like the kind found in cellular phones; all things that an engineer does not want in a properly functioning well planned PCB. Ironically, these examples are all the same mistakes made in the first draft of this board, see figure 3.

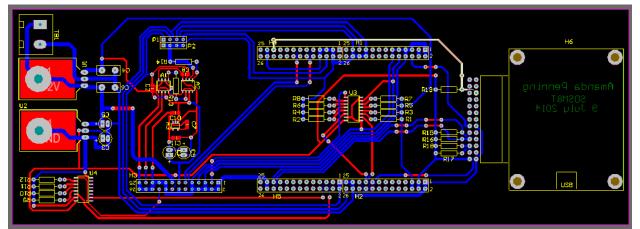

This design phase included several revision phases. The more carefully thought out and planned at the beginning, the much easier and quicker the revisions will be. As stated previously, size matters when building circuit boards and for commercial boards the smaller the layout the better. But in the interest of proper signal shielding, total board size became less of an issue for this design; see figures 4, 5, and 6.

Figure 3: First version of mother board with unintended crosstalk errors.

Figure 4: Revision 2.

Figure 5: Revision 4

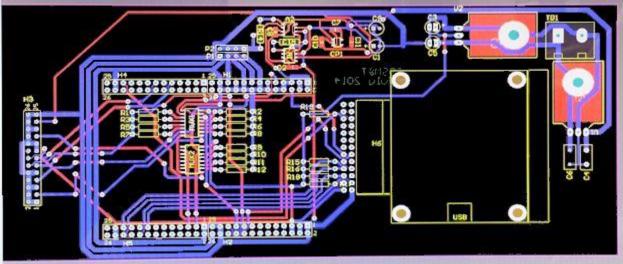

Figure 6: Final mother board layout. Blue lines represent traces on the bottom side of the board. Red lines represent traces on the top side of the board. Yellow lines represent the outline or 'footprint' of the components. Final board size is 9.5 by 3.25 inches.

All of the noise generating and amplifying components have been moved to the left, inside of the main input signal line, but far enough away that interference should be minimal. Ideally, it would have been best to set them outside of the signal lines, but then there would have been crossing of signal lines, which is counterproductive for this venture. All of the signal lines, the three main inputs, the amplified input, and the measurement line have been heavily shielded on both sides with traces double the standard width. Careful care has been given to ensuring that no signal lines cross over each other. The few lines that do cross are command lines from the controller or power lines and have been carefully done so at a 90 degree angle in order to minimize magnetic field coupling. (9) All traces have been carefully placed to create no acute angles; acute angles can be problematic in the milling or etching stage as well as create interference problems. (12) It is also important that all traces take the shortest route possible, but they also must be longer than 1/3 the rise time of the wavelength, or else ringing may occur. (10) Again, for the sake of not crossing any signal lines, the traces are longer than they would be normally, which can be problematic because it can allow more opportunity for electromagnetic coupling. But because all of the signals are heavily shielded and spaced apart, it should not be a problem. A final consideration before laying the traces is their width. Trace (conductor) width and thickness are determined by the signal characteristics, current carrying capacities required, and the maximum allowable temperature rise. These specifics are determined by safety organizations such as Underwriters Laboratories. (7) Clearly, the final board layout is entirely different than the original, see figure 6.

#### **3.3 Daughter Board Design**

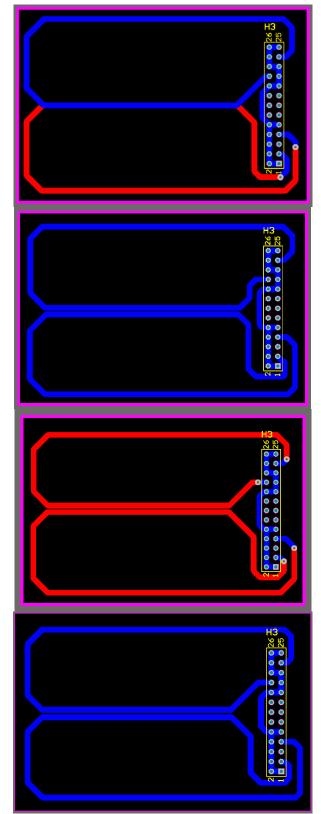

Once the mother board was completed, it was time to consider designs for the daughter boards. 'Daughter board' is a term used in electronics to signify a board that is plugged into a larger board, usually referred to as a mother board. There are many colloquial names such as daughter card, mezzanine board, piggyback board, all referring to the same thing. These boards are where the intentional crosstalk will occur. The crosstalk will be created by turning off the 'rules' in the design program and laying the traces as close together as possible. Due to constraints of the milling machine, the narrowest gap between traces that could be accomplished is 8 thousandths of an inch (0.008 inches). In the first daughter board (DB1), the aggressor and victim traces are both on the bottom side of the board, separated by 8 thousandths of an inch. The second board (DB2), the aggressor trace is on the bottom and the victim trace is on top, directly over the aggressor. Both boards are 2 by 3 inches. Two other daughter boards have been designed but have not yet been milled due to the fact that none of the current two have been tested yet to see if they function as planned. The third has both traces on the top side separated by 8 thousandths of an inch; the idea is to see if something as simple as the side the traces are placed on will have an effect on the amount of crosstalk picked up. The fourth has both traces on the bottom side separated by 16 thousandths of an inch.

Figure 7: (From top to bottom) Daughter board 1, 2, 3, and 4.

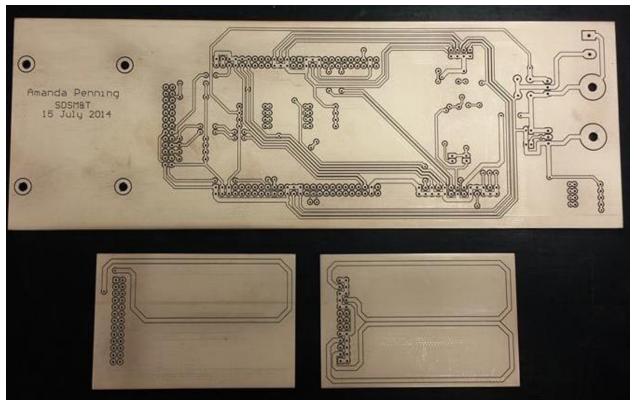

# 3.4 Board Milling

After final revision and approval, the boards were milled. Using milling machine LPKF ProtoMat C60, Mr. Steven Lawler, an electronics specialist with the school, milled the mother board and the first two daughter boards. It took approximately 90 minutes to mill the mother board and only about 20 minutes per daughter board.

Figure 8: Milled mother board (top), milled daughter board 2 (bottom left) milled daughter board 3 (bottom right).

#### 3.5 Board Assembly

Once milling was completed, the task of populating the board began. Using a Weller WES51 soldering iron and a Weller ETS-ET series 1/64 inch long conical tip, the components were soldered onto the board. The process of soldering itself is not difficult but there is an order of precedence when populating a board. First, the vias must be soldered. Vias are tiny holes used to create an electrical connection between physical layers in an electronic circuit; they transfer the circuit from one side of the board, or layer, to another. The boards in this experiment are only two layer boards, FR-4; 0.059 inch thick (not including copper) with one ounce copper on both sides. In commercial boards, the vias as well as the holes for axilated components are electroplated with copper and then plated with a very thin layer of tin to increase solderability of the components. Electroplating is a process by which copper is plated through the drilled holes; this completes the circuit from one layer to another. The process of electroplating is not available at the school and so instead, the connections through vias have to be made physically using small pieces of wire. This is done first because, at times, vias are very close to other components and it can be difficult to reach them if the other components are placed first. Though every effort is made to avoid it, sometimes vias have to be placed under other components and therefore must be soldered first. Via connections were made using pieces of wire approximately 0.006 inch in length. They were inserted into the via hole and soldered from both sides to complete the circuit. There were a total of 62 vias on the mother board. After the vias are soldered, the order of precedence becomes more a personal choice for the one doing the soldering. Most choose to solder the surface mount components first and that is what was done in this case. Soldering surface mount parts is a very precise operation. The component must be orientated correctly to ensure proper electrical connection and functioning. It must also be

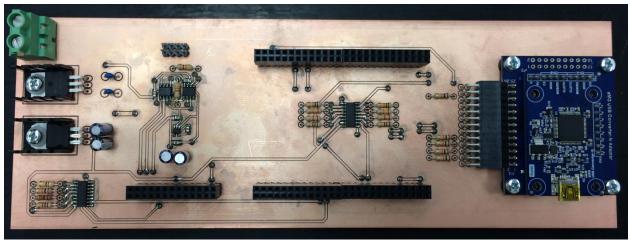

centered precisely on the pads. The feet must be centered between the long and short edges, allowing for a proper solder fillet to form. (6) There are tolerances for placement but the more exact the better for longevity of the circuit as a whole. While soldering the surface mount components it was found that two of the components had pads that were too small, Op Amps A1 and A2. They were just large enough to get a solder connection however; in future builds the size of the pads must be enlarged. The pad size for all other surface mount parts was more than sufficient. After soldering the surface mount components, the through- hole components were soldered. There are also IPC standards for the soldering of these components, but due to the fact that the through holes on this board are not plated it is not feasible to hold them to those standards. Instead, to ensure good electrical connection, the pads of the through-hole components were enlarged, offering a larger surface area to be soldered. Again, one must ensure the proper orientation of polarized components. All through-hole components on these boards where soldered on the bottom side only as it was intentionally designed. Once all components were soldered, the aMG USB Converter-N Adapter<sup>™</sup> was installed to interface between the test boards and the computer. Figure 9 is the completed board, without the STM32 F4 Discovery<sup>TM</sup> micro-controller, in order to show the components that are underneath it. This board will be used to generate the input signal and measure the return signal. It is pictured below the mother board, figure 10.

Figure 9: Populated mother board.

Figure 10: Discovery Board.

The STM32 F4 Discovery<sup>™</sup> micro-controller is an external board that is programmed to drive the signals for the test boards. The signals generated will either be analog, digital or pulse width modulation (PWM). An analog signal is continuous, meaning there are no breaks or interruptions, and the wave is symmetrical and sinusoidal. A digital signal is not continuous. It is symmetrical but the wave shape is square or rectangular; the crests and troughs are the exact same shape just inverted. Or, to put it another way, when the wave form is a crest it is 'on' and

when it is a trough it is 'off.' A PWM signal is a way to get an analog result using digital means. Digital control is used to switch a signal on and off, creating a square wave. Unlike a purely digital signal where the time spent on equals the time spent off, a PWM signal can be shaped to fit the needs of the circuit; the programmer decides how much time is spent on and off. It can be programmed to spend 90% of a cycle on and only 10% off, or vice versa, any pattern that is needed. (2) Analog signals are much more susceptible to noise like crosstalk, as a comparison the capability to select digital and PWM signals were included so the difference could be readily seen. It also allows more room for future expansion of the experiment.

#### 3.6 Materials

Circuit boards: FR-4; 0.059 inches thick (excluding copper) with one ounce copper both sides.

1.5 GHz, high speed Op Amp

Polarized Capacitor (Radial) 10uF

Capacitor .1uF

Polarized Capacitor (Radial) 10uF

Capacitor .22uF

Capacitor 1uF

5 pin, unregulated 60-mA voltage inverter (Charge Pump)

Header, 13-Pin, Dual row, Stackable

Header, 13-Pin, Dual row 90°

# Heat sink

16 pin, dual single-pole 4:1 analog switch (MUX)

Header, 4-Pin

Resistors, 110Ω, 430Ω, 510Ω, 1KΩ, 2.4KΩ, 10KΩ, 25KΩ, 50KΩ, 100KΩ

Term Block, 2 Position, 32 Amp Connector

Three-Terminal Positive Voltage Regulator +5V

3 Amp Adjustable Regulator 3.3V

# 3.7 Equipment

Altium Designer® version 2010

LPKF ProtoMat C60 Milling Machine

Weller WES51 Soldering Iron

Weller ETS-ET series 1/64" long Conical Tip

Chemtronics No-Clean Tacky Flux

Kester No-Clean 245 Solder Wire, 0.015"

Solder-Wick No-Clean SD 0.080" ESD 5' Spool

Standard Adjustable Wrist Strap with 6' Coil Cord

Stainless Steel Anti-Magnetic Economy Tweezers with Straight Ultra-Fine Point

Tektronix TDS 2004B Oscilloscope

STM32 F4 Discovery<sup>TM</sup> Micro-Controller

aMG USB Converter-N Adapter™

#### 4. Results

At this time, no tests have been run due to the fact that the design and layout of the mother board took much longer than anticipated. There has also been a snag in programming the Discovery board. It was discovered that the digital to analog converter on the board can only reach a frequency of 2 MHz, but in order to test crosstalk the frequency needs to be above 16 MHz. The attempt is being made to input simple bits to toggle on and off, creating an artificial square wave. If this works, then only the digital and PWM lines will be able to be tested.

#### 5. Discussion

Though the scope of this experiment began with a study of crosstalk, it morphed into something much deeper. As research into the phenomenon was conducted, it was concluded that in order to properly complete this experiment, much more was needed than just createing crosstalk. It became increasingly clear that the signals routed into the test boards needed to be protected from outside interference that could skew the results. It also became clear that once the crosstalk was created, the signal coming back to be measured also had to be protected from loss of integrity. This required the construction of a mother board that was adaptable to future experiments while maintaining sound electrical engineering principles.

Unfortunately, while attempting to see if the programming work-around would function, it was discovered that two sets of pins on the footprint for the connectors that mate with the Discovery board were mismatched. It is unclear how PB1 and PA5 were mismatched as the footprint was taken from an existing library. However, the fix was easy enough; the line to PB1 was cut and a jumper installed from the trace to PA5. Another design error discovered at this time was that the 5V and the 3.3V lines were switched. Again, it is unclear how this mistake was made but this solution was also simple; the existing traces were cut and jumper wires were added to the correct pins.

#### 6. Conclusion

Based on the research, the data should show that when spacing between the traces is increased, the amount of voltage induced on the victim trace will decrease. Similarly, when a shield trace is placed between the aggressor and victim traces the instance of crosstalk will decrease.

#### 6.1 Future Work

There is much that can be done with this experiment in the future. It was designed for that very purpose, and also the greater purpose of allowing future electrical engineering students an opportunity for hands on experience with the types of crosstalk and the difference board layout and design make. The next step in this process will be to conduct initial tests to ensure that the fixes to the design of the mother board worked and that it functions correctly, followed by testing the first daughter boards. After that, design and testing of additional daughter boards, measuring the impact of trace placement and shielding. Once it is certain that the mother board and daughter boards behave as expected, the third step will be to add nichrome wires to simulate heat noise. Subsequently, the experiment could be expanded by adding electrical components to the daughter boards and measuring their effect on the crosstalk signals. Finally, altering the input signal and measurement signal using the resistor bank to see the effect on crosstalk. A final note on design: if this mother board is to be reproduced in the future, the solder pads for A1 and A2 need to be made larger. Though a good electrical connection was able to be made, the pads are not large enough to allow for a proper solder fillet to form. Once these have all been completed, the process of developing an undergraduate laboratory experiment can begin.

#### References

- Analog, Embedded Processing, Semiconductor Company, Texas Instruments TI.com.

(n.d.). Analog, Embedded Processing, Semiconductor Company, Texas Instruments TI.com.

Retrieved July 21, 2014, from <u>http://www.ti.com</u>

- 2) Arduino PWM. (n.d.). Arduino PWM. Retrieved July 21, 2014 from,

http://arduino.cc/en/Tutorial/PWM

3) Basic Electronics Tutorials and Revision. (n.d.). Basic Electronics Tutorials. Retrieved July

11, 2014, from http://www.electronics-tutorials.ws

4) Carlsson, J. (1994). *Crosstalk on Printed Circuit Boards*. (2<sup>nd</sup> ed ). Retrieved June 11, 2014, from <u>http://www.sp.se/sv/index/research/EMC/</u>

5) Common Impedance Coupling. (n.d.). *LearnEMC: Introduction to EMC*. Retrieved July 11, 2014 from

http://www.learnemc.com/tutorials/Common\_Impedance\_Coupling/conducted\_coupling.html

- 6) IPC-A-610. Acceptability for electronic assemblies (Revision D. ed.). (2005). Bannockburn,III.: IPC.

- 7) IPC-2221. Generic Standard on printed board Design. (2003). Northbrook, IL: IPC.

- 8) Scearce, S. (n.d.). PCB Carolina 2014. PCB Crosstalk Fundamentals and Strategy. Retrieved

- July 21, 2014, from http://pcbcarolina.com/images/sscearce-talkx-ipc.pdf

9) Serway, R.A. (1986). Wave Motion. Physics for scientists & engineers, with modern physics(2nd ed., pp. 345-362). Philadelphia: Saunders College Pub.

10) Tutorial-Getting Started with PCB Design. (n.d.). *Tutorial*. Retrieved June, 16, 2014, from <a href="http://techdocs.altium.com/display/ADOH/+Getting+Started+with+PCB+Design">http://techdocs.altium.com/display/ADOH/+Getting+Started+with+PCB+Design</a>

UNDERSTANDING HOW VOLTAGE REGULATORS WORK Voltage Regulator

General Design Fundamentals. (n.d.). Understanding How Voltage Regulators Work. Retrieved

July 21, 2014, from

http://www.analog.com/en/content/ta\_fundamentals\_of\_voltage\_regulators/fca.html

12) Welcom | Omni Printed Circuit Boards. (n.d.). Welcom | Omni Printed Circuit Boards.Retrieved July 21, 2014 from <u>http://www.omnicircuitboards.com</u>

# Acknowledgments

This work was made possible by the National Science Foundation REU Site: Bringing Us Together, Improving Communications and Lives EEC-1359476. Thank you to Mr. Steven Lawler, for his guidance and assistance, as well as the students in the Controls Lab, especially Conrad Farnsworth for helping with circuit design, and Adrian Del Grosso for programming the micro-controller. Thank you also to Dr. Melody Jewell, for the recommendation to this program. Finally, thank you to the NSF for providing this opportunity.